- 您现在的位置:买卖IC网 > Sheet目录311 > AS1117-BQFT (ams)IC DRIVER 64LED MOBILE 24-TQFN

�� �

�

�

�AS1117�

�Datasheet� -� D� e� t� a� i� l� e� d� D� e� s� c� r� i� p� t� i� o� n�

�I2C� Interface�

�The� AS1117� supports� the� I2C� serial� bus� and� data� transmission� protocol� in� high-speed� mode� at� 3.4MHz.� The� AS1117�

�operates� as� a� slave� on� the� I2C� bus.� The� bus� must� be� controlled� by� a� master� device� that� generates� the� serial� clock�

�(SCL),� controls� the� bus� access,� and� generates� the� START� and� STOP� conditions.� Connections� to� the� bus� are� made� via�

�the� open-drain� I/O� pins� SCL� and� SDA.�

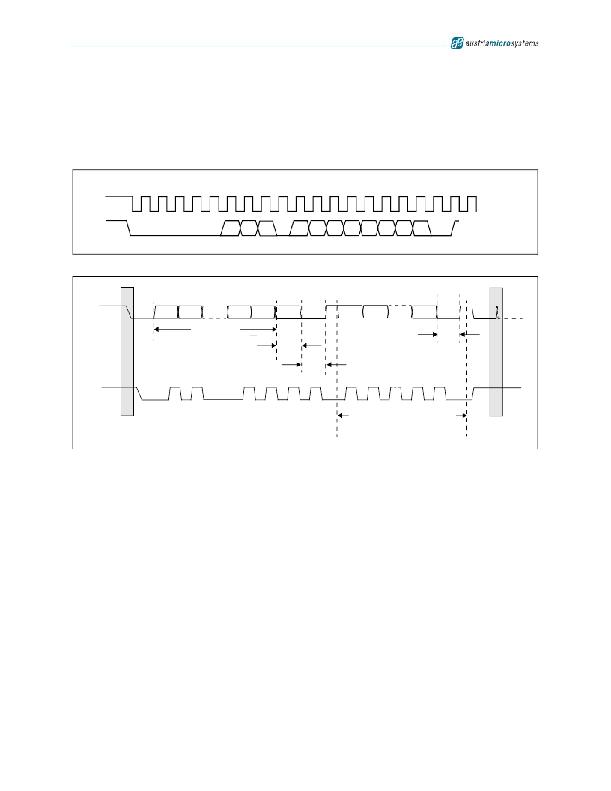

�Figure� 18.� I2C� Interface� Initialisation�

�1�

�8�

�9�

�1�

�8�

�9�

�0�

�0�

�0�

�0�

�0�

�A1�

�A0� R/W�

�D15� D14� D13� D12� D11� D10�

�D9�

�D8�

�Default values at power up: A1 = A0 = 0�

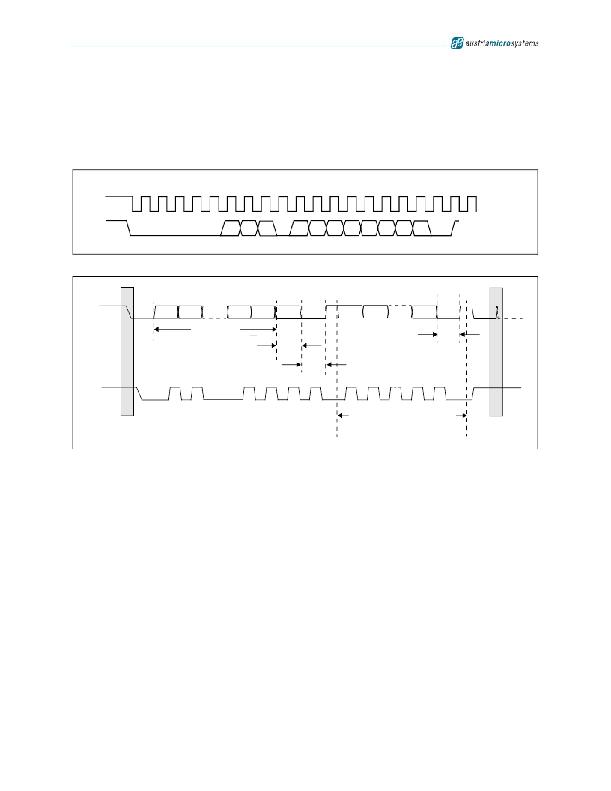

�Figure� 19.� Bus� Protocol�

�SDI�

�MSB�

�Slave Address�

�R/W�

�Direction� Bit�

�ACK� from�

�Receiver�

�ACK� from�

�Receiver�

�SCL�

�1�

�2�

�6�

�7�

�8�

�9�

�1�

�2�

�3-8�

�8�

�9�

�START�

�ACK�

�ACK�

�Repeat if More Bytes Transferred�

�STOP� or�

�Repeated�

�START�

�The� bus� protocol� (as� shown� in� Figure� 19� )� is� defined� as:�

�-� Data� transfer� may� be� initiated� only� when� the� bus� is� not� busy.�

�-� During� data� transfer,� the� data� line� must� remain� stable� whenever� the� clock� line� is� HIGH.� Changes� in� the� data� line�

�while� the� clock� line� is� HIGH� will� be� interpreted� as� control� signals.�

�The� bus� conditions� are� defined� as:�

�-� Bus� Not� Busy� .� Data� and� clock� lines� remain� HIGH.�

�-� Start� Data� Transfer� .� A� change� in� the� state� of� the� data� line,� from� HIGH� to� LOW,� while� the� clock� is� HIGH,� defines� a�

�START� condition.�

�-� Stop� Data� Transfe� r.� A� change� in� the� state� of� the� data� line,� from� LOW� to� HIGH,� while� the� clock� line� is� HIGH,�

�defines� the� STOP� condition.�

�-� Data� Valid� .� The� state� of� the� data� line� represents� valid� data,� when,� after� a� START� condition,� the� data� line� is� stable�

�for� the� duration� of� the� HIGH� period� of� the� clock� signal.� There� is� one� clock� pulse� per� bit� of� data.�

�Each� data� transfer� is� initiated� with� a� START� condition� and� terminated� with� a� STOP� condition.� The� number� of� data�

�bytes� transferred� between� START� and� STOP� conditions� is� not� limited� and� is� determined� by� the� master� device.�

�The� information� is� transferred� byte-wise� and� each� receiver� acknowledges� with� a� ninth-bit.�

�Within� the� I2C� bus� specifications� a� high-speed� mode� (3.4MHz� clock� rate)� is� defined.�

�-� Acknowledge� :� Each� receiving� device,� when� addressed,� is� obliged� to� generate� an� acknowledge� after� the� recep-�

�tion� of� each� byte.� The� master� device� must� generate� an� extra� clock� pulse� that� is� associated� with� this� acknowledge�

�bit.� A� device� that� acknowledges� must� pull� down� the� SDA� line� during� the� acknowledge� clock� pulse� in� such� a� way�

�that� the� SDA� line� is� stable� LOW� during� the� HIGH� period� of� the� acknowledge� clock� pulse.� Of� course,� setup� and�

�hold� times� must� be� taken� into� account.� A� master� must� signal� an� end� of� data� to� the� slave� by� not� generating� an�

�www.austriamicrosystems.com/LED-Driver-ICs/AS1117�

�Revision� 1.00�

�9� -� 23�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AS1118-BQFT

IC DRIVER 64LED W/DELAY 24-TQFN

AS1121B-BQFT

IC DRIVER 16-CH 32-TQFN

AS1122B-BQFT

IC LED DVR 12-CH 24-TQFN

AS1123-BTST

IC LED DVR 16-CH 40MA 24-QSOP

AS1390A-ZQFT

IC BOOST CTLR/BUCK CONV 20-QFN

AS212-L

SOCKET 12V AUTO SAFETY CAP MNT

AS212C

AUTO 12V SOCKET W/SAFETY CAP

AS212

SOCKET AUTO LOCKING BLACK

相关代理商/技术参数

AS1117M1

制造商:ALPHA 制造商全称:ALPHA 功能描述:800mA Low Dropout Regulator SCSI-II Active Terminator

AS1117M1-X

制造商:ALPHA 制造商全称:ALPHA 功能描述:800mA Low Dropout Regulator SCSI-II Active Terminator

AS1117M3

制造商:ALPHA 制造商全称:ALPHA 功能描述:800mA Low Dropout Regulator SCSI-II Active Terminator

AS1117M3-1.5

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC

AS1117M3-2.5

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC

AS1117M3-3.0

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC

AS1117M3-3.3

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC

AS1117M3-5.0

制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC